意昂体育平台人工智能研究院類腦智能芯片研究中心唐希源研究員課題組在國際集成電路設計領域頂級會議IEEE Custom Integrated Circuits Conference(CICC)上發表論文“A Calibration-Free 15-level/Cell eDRAM Computing-in-Memory Macro with 3T1C Current-Programmed Dynamic-Cascoded MLC achieving 233-to-304-TOPS/W 4b MAC”,發布了一種最新研製並實現的基於65nm CMOS工藝的電流型eDRAM模擬存內一體芯片,該創新工藝通過將模擬權重的編程與計算統一到電流域,大幅提高了模擬存算一體電流的計算精度與魯棒性🤘🏿。

不斷發展的AI算法對邊緣端硬件的算力與能效提出挑戰🫀🧖🏻。傳統計算架構執行算法的瓶頸在於數據搬運功耗🧛🏿,即“存儲墻”問題。為解決這一問題✣,將計算嵌入到存儲單元中並在模擬域完成乘累加運算的模擬存算一體芯片被提出🐰。模擬域存算一體芯片可以分為電流型設計🛁、電荷型設計以及時間型設計👩🏻🌾。其中,電流型設計可以模擬計算因其高面積效率和高並行等特點⚰️🤴🏿,受到研究人員的青睞。

盡管近年不斷有新型電流型存算一體芯片被提出📸, 然而電流型存算一體芯片的根本問題並未得到解決🪩。目前的電流型模擬存算一體芯片受到晶體管非理想性的限製,無法在小電流下實現精確計算🥿,因而存在著計算精度、能效瓶頸與魯棒性多重挑戰👌🏿,其應用場景嚴重受限。

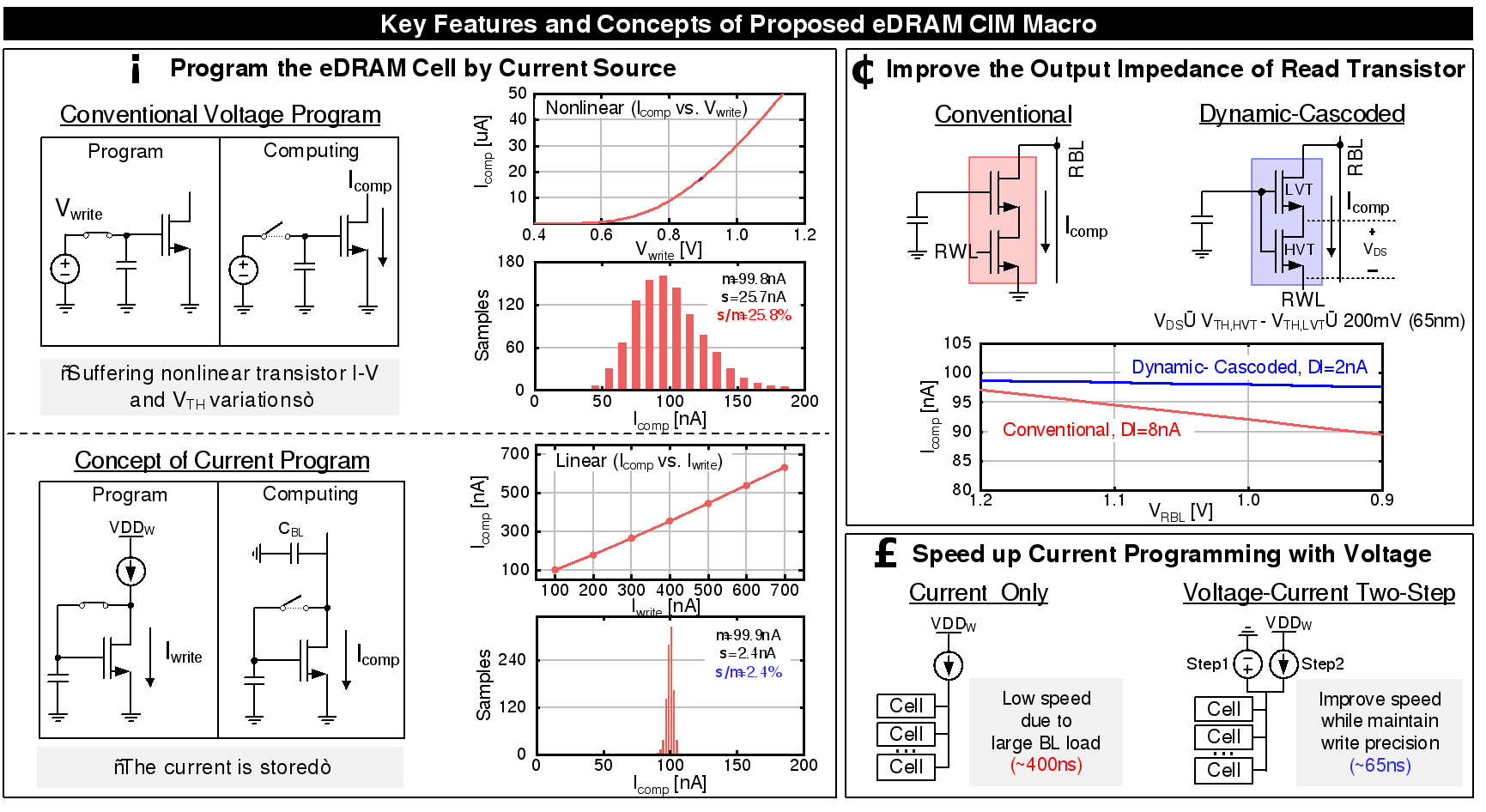

針對這一系列挑戰🤾🏻♀️🦚,唐希源課題組從電流型模擬存算一體電路的誤差產生機製入手🧑🏼🦱,首次提出電流編程技術。如圖1所示,該技術利用編程電流產生自校準的權重電壓🧑🏿🎓,實現多值模擬權重的高精度編程。同時✊🏽,課題組提出電壓-電流兩步編程模數,利用編程電壓進行快速初步寫入並用編程電流完成精確寫入,大幅提高了多比特權重編程速度。此外⚇,課題組提出自偏置共源共柵讀出結構,在無需額外偏置電路的情況下大幅增加了存儲單元讀出精度🏃🏻♀️➡️,降低了計算電流的對位線電壓的敏感度。這三項技術使得電流型多值模擬存算單元可以無需校準地工作在小於1uA的計算電流下🙆🏿♂️,突破了電流型存算一體電路的精度與能效瓶頸,並大幅提升其魯棒性。

圖1 所提出電流型存算一體設計的關鍵技術

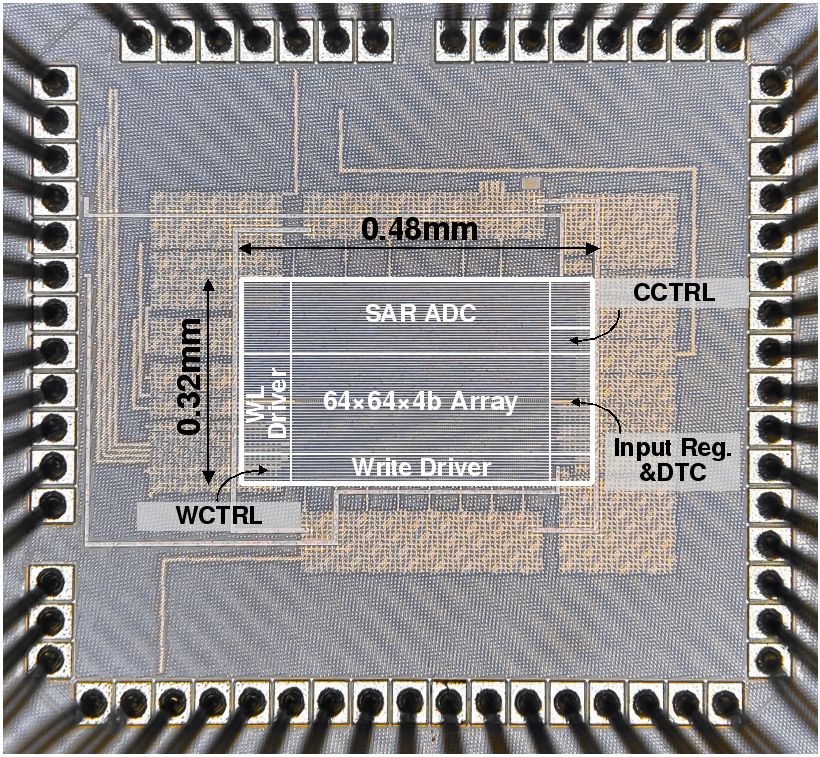

基於上述創新設計🧔🏻♂️,課題組研製了一款基於65nm CMOS工藝的電流型eDRAM模擬存內一體芯片(圖2),並對芯片進行了性能測試與匯報🧧。在4-b輸入/4-b權重/5-b輸出精度的情況下,16Kb容量的原型芯片實現了233~304 TOPS/W的計算能效與2.963 TOPS/mm2的單位面積算力🔚,達到電流型存算一體芯片中的國際領先水平🧛🏽♂️。該創新通過將模擬權重的編程與計算統一到電流域,大幅提高了模擬存算一體電流的計算精度與魯棒性。

圖2 電流編程存算一體芯片顯微照片

意昂体育平台博士後宋嘉豪為第一作者🤛🏻,唐希源與王源教授為通訊作者。